FT2232のFT245 FIFOモードを使うときの留意点

GRWOTH FPGA/ADCボードでは、USBインタフェースとしてFuture Technology社のFT2232Hを搭載しています。FT2232は、USB2の高速伝送(最高40MBytes/s)に対応したシリアル-USB変換とパラレル-USB変換を2ch搭載したインタフェース変換ICで、秋月ではUSBコネクタ付きのFT2232Dのモジュール版が1450円で販売されています。

チップ単体で720円(RS)と安価で、高速通信できる仮想COMポートが2ポート取れるので、自作FPGAボードを作るときにとても便利なチップです。

A側とB側の2つのChannelは、それぞれ独立した仮想COMポートとしてMacからは認識されます。デフォルトでは、FT232のようなRS232非同期シリアル-USB変換インタフェースとして動作します。外部に設定保存用のEEPROMを付けて、FTProgというWindows用の設定ソフトウエアから設定を書き込むと、Channel AはRS232非同期シリアルモード、Channel BはFT245 Asynchronous FIFOモードで動作させることができます。このモードだと、使用時に専用ドライバ(libftd2xx)からの設定は不要で、普通の仮想COMポートとして認識されつつも最大8MBytes/sくらいの伝送ができてとても便利です(Rubyのシリアル通信ライブラリやboostから使えるので、ポータビリティも高い)。

FT245 Synchronous FIFOモードでは、最大40 Mbytes/sという高速通信ができます。ただFT245 Synchronous FIFOモードを使うためには、EEPROMとFTProgからの設定に加えて、ソフトウエア側からのモード設定変更が必要なのと、Channel Bしか使えなくなる(Channel A側のバッファなどが内部的にChannel Bの通信用に使用されるため)、データ送受信もlibftd2xxの関数を用いて行う必要がある(i.e. 仮想COMポートとしては使えない)という点がややネックですが、これらの手間をおぎなってあまりある通信速度なのでしかたないですね。

FT245 FIFOモードを使うときの留意点

実際にFT245 FIFOモードのFPGA側のインタフェースを記述するときに設定内容で少し混乱したのでメモしておきます。

- FT245-likeなFIFOモードとして使用するときは、外付けのEEPROMが必要。

- FT245-likeなFIFOモードとして使用するときは、FTProg等の専用の設定ソフトで、EEPROMにモード設定を書き込んでおく必要がある。

- FT245-likeなFIFOとして動作するモードはSynchronous FIFOとAsynchronous FIFOの2つのモードがある。

- FT245 FIFOモードに設定してある場合、電源投入後はFT245 Asynchronous FIFOモードで起動する。この状態で、何もしなくても非同期モードでの通信は可能。

- FT245 Synchronous FIFOモードで通信したいときは、

FT245 Asynchronous FIFOモードの通信手順

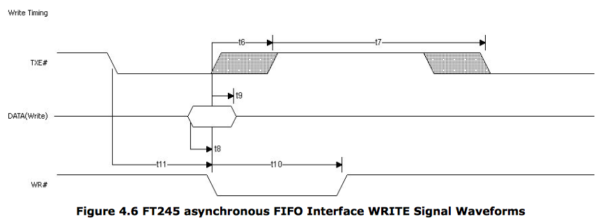

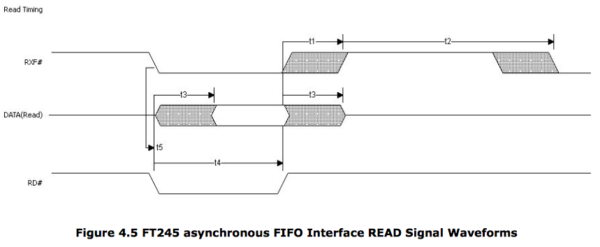

詳細はFT2232のデータシートを参照してください。以下の図はデータシートから引用しています。

FPGA→FT2232 (→Mac/Raspberry Pi)方向の通信(FPGAからデータを送信)

書き込み許可信号TXE#がLow(書き込みOK)になったら、データをDataに出して、WR#をHigh→Low(書き込み実行)にする。t10 (30ns)以上待ってから、WR#をHighに戻す。TXE#がLowになったら、次の書き込みが可能になる。

Dataラインが書き込み操作と読み出し操作で共有されている(inoutになる)ので、FPGAでこのインタフェースを実装するときは、ステートマシンでDataの状態を管理するほうがきれいだと思います(組み合わせ回路だとメンテナンスしづらい)。

(Mac/Raspberry Pi→)FT2232→FPGA方向の通信(FPGAでデータを受信)

FT2232にMac/Raspberry Piからデータが届くと、RXF#がLow(データ有り)になる。FPGA側でRXF# == Lowを確認したら、RD#をHigh→Low(データ読み出し)に遷移させる。t3 (1〜14ns)後にDataラインにデータが出てくるので、適当な時間だけまってからDataをラッチ。RD#をHigh(データ読み出し終了)に戻すとt1(1〜14ns)後にRXF#がLow→High(データ無し)に戻る。次のデータ有り(RXF# == Low)になるまで、最低49nsの時間がかかる。

タイミング仕様

TXE#やRXF#の状態チェックと、WR#やRD#の制御の際には、以下のタイミングを守れるように、FPGAで使用しているクロックに合わせて適当なwaitを入れる必要があります。

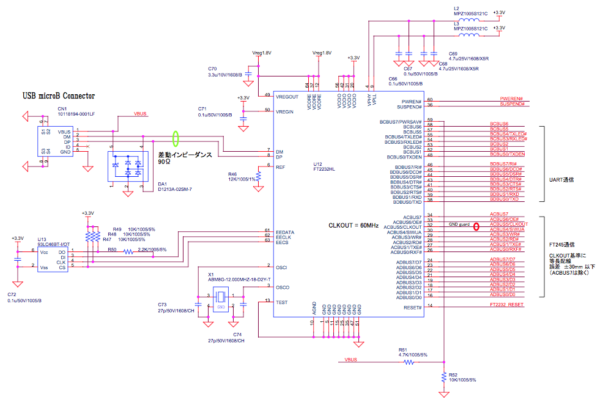

サンプルの回路図

GROWTH FPGA/ADCボードでは以下のように結線しています。回路図はシマフジ電機提供です。ボードを買いたいという人はYuasaかEnotoさんまでお気軽に連絡してください。

参考サイト